State 4: Clock – HIGH S’ – 1 R’ – 1 Q – 1 Q’ - 1įor the State 4 inputs the RED led and GREEN led glows indicating the Q & Q’ to be HIGH. State 3: Clock – HIGH S’ – 0 R’ – 1 Q – 0 Q’ - 1įor the State 3 inputs the RED led glows indicating the Q’ to be HIGH and GREEN led shows Q to be LOW. State 2: Clock – HIGH S’ – 1 R’ – 0 Q – 1 Q’ - 0įor the State 2 inputs the GREEN led glows indicating the Q to be HIGH and RED led shows Q’ to be LOW. State 1: Clock – HIGH S’ – 0 R’ – 0 Q – 0 Q’ – 0įor the State 1 inputs, the RED led glows indicating the Q’ to be HIGH and GREEN led shows Q to be LOW. Hence, default input state will be S’=0, R’=0.īelow we have described the all four states of SR Flip-Flop using SR flip flop circuit made on breadboard. The pins S’ and R’ are normally pulled down. The truth table and corresponding states varies according to the type of construction which can be either using NAND gates or NOR gates. Thus, for different input at S’ and R’ the corresponding output can be seen through LED Q and Q’. Hence, the regulated 5V output is used as the Vcc and pin supply to the IC. The 9V battery acts as the input to the voltage regulator LM7805. The two LEDs Q and Q’ represents the output states of the flip-flop. The two buttons S (Set) and R (Reset) are the input states for the SR flip-flop. Hence, we have used a LM7805 regulator to limit the supply voltage and pin voltage to 5V maximum. The IC power source has been limited to MAXIMUM OF 6V and the data is available in the datasheet. Here we have used IC SN74HC00N for demonstrating SR Flip Flop Circuit, which has four NAND gates inside. SR Flip-flop Circuit Diagram and Explanation: Below is the pin diagram and the corresponding description of the pins. It is a 14 pin package which contains 4 individual NAND gates in it. The IC used is SN74HC00N (Quadruple 2-Input Positive-NAND Gate).

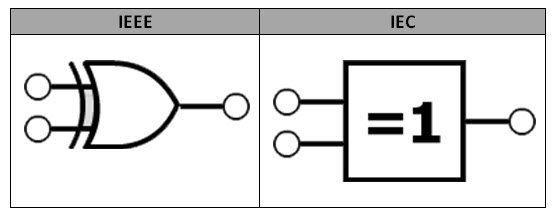

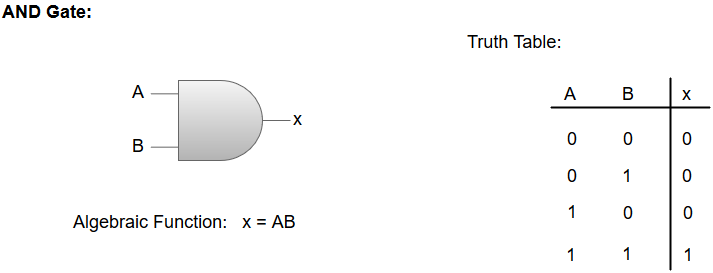

We are constructing the SR flip flop using NAND gate which is as below, But, the important thing to consider is all these can occur only in the presence of the clock signal. According to the table, based on the inputs, the output changes its state. The Q and Q’ represents the output states of the flip-flop. The S (Set) and R (Reset) are the input states for the SR flip-flop. The memory size of SR flip flop is one bit. Thus, the output has two stable states based on the inputs which have been discussed below. Again, this gets divided into positive edge triggered SR flip flop and negative edge triggered SR flip-flop. Thus, SR flip-flop is a controlled Bi-stable latch where the clock signal is the control signal. The clock has to be high for the inputs to get active. Whenever the clock signal is LOW, the inputs S and R are never going to affect the output. Here we are using NAND gates for demonstrating the SR flip flop. Either of them will have the input and output complemented to each other. SR latch can be built with NAND gate or with NOR gate. But now-a-days JK and D flip-flops are used instead, due to versatility.

#Nand x or truth table portable#

SR Flip-flops were used in common applications like MP3 players, Home theatres, Portable audio docks, and etc. Here in this article we will discuss about SR Flip Flop and will explore the other Flip Flop in later articles. Out of the above types only JK and D flip-flops are available in the integrated IC form and also used widely in most of the applications.

0 kommentar(er)

0 kommentar(er)